Hello,

I am trying to run the R Series - NI SPI FPGA Simulation.lvproj project example that comes with NI SPI IP on an actual PXIe-7976R FlexRIO FPGA target with an attached NI 6581B Digital Adapter Module. The example is for a PCIe-7841R but I ported it over to my FPGA target following these steps and made additional modifications to try to make it work with my set-up. I learned that CLIPs for FlexRIO FAMs don't work with Desktop Exection Nodes so I know that I cannot simulate the project as originally intended so I am trying to use FPGA I/O node host side (open FPGA vi reference) to implement on actual hardware.

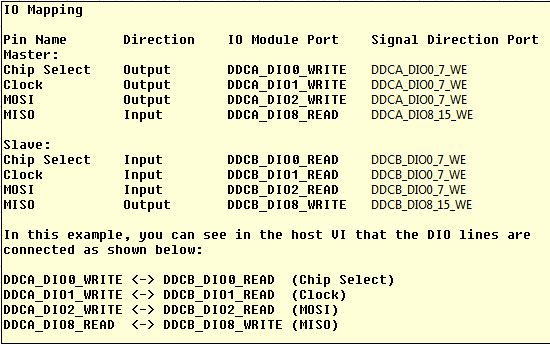

My first question is regarding my adapter module IO configuration and selection. I've added the IO Module (NI 6581B : NI 6581B Channel) to my project and selected the channels as shown in the table below. I have an actual physical hardware connection as descibed below using two NI SHC68-C68-D4 cables and a break-out board.

I changed the names as well:

I selected these DIO channels because I wanted the DDCA Connector to be the Master and the DDCB Connector to be the Slave. Also, in this CLIP each grouping of eight I/O channels has a write enable signal. I did not use the Port configuration because I needed 4 available DIO channels and I only saw DIO0-3. Is my logic for selecting Channel vs Port correct here?

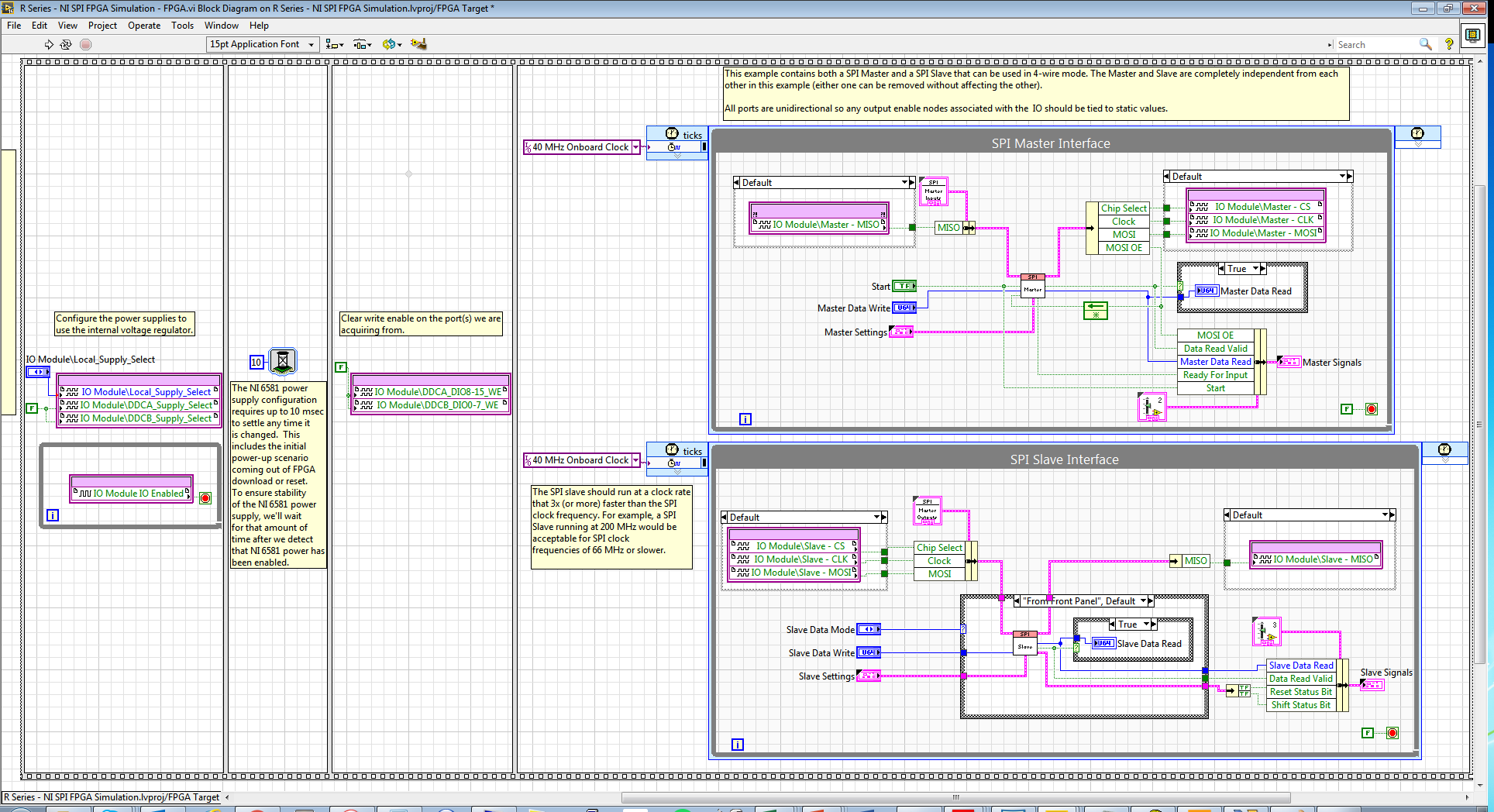

Following the same strategy as the FlexRIO/NI6581B examples, I modified the FPGA.vi to include some initialization outside of the timed loops:

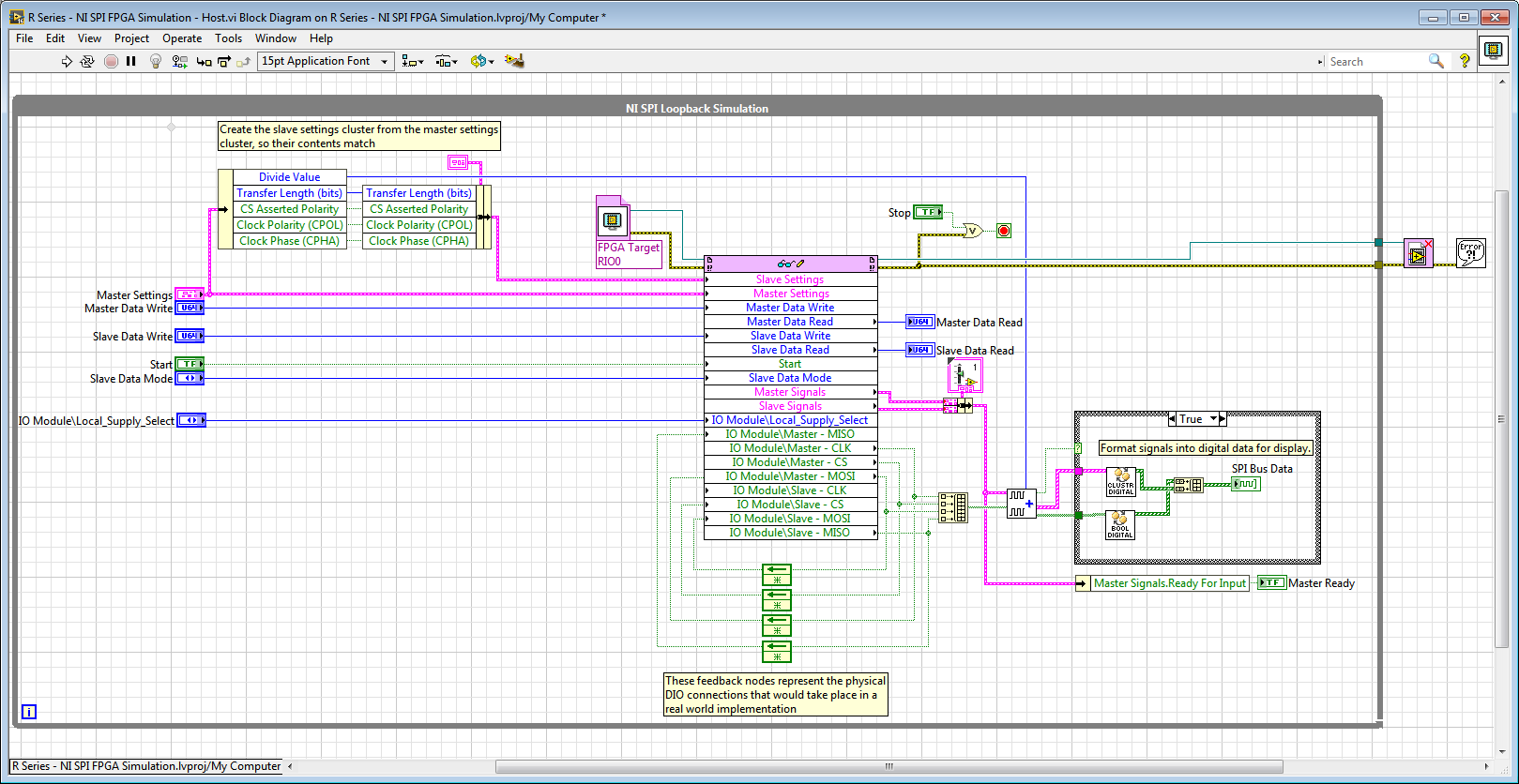

And in the Host.vi I have a FPGA reference node and have wired the feedback loops accordingly:

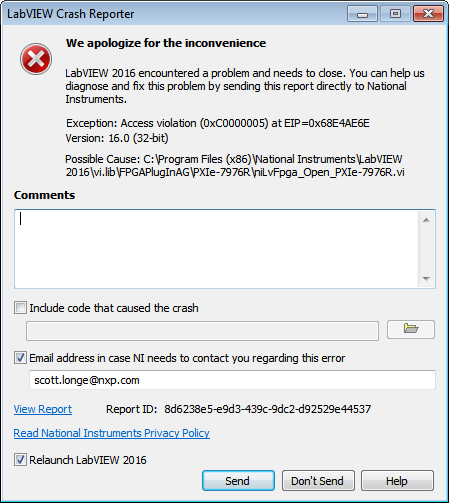

When I compile the FPGA and try to run Host.vi LabVIEW inevitably crashes with the Crash Reporter below and and has to restart:

Does anybody know what I am doing wrong here? My guess is that it has something to do with the CLIP/IOModule. Any help is appreciated.

Thank you,

Scott