Hi, does anyone have any idea how to configure camera (framerate, 8x8 mode, resolution and so on) having framegrabber FPGA Module and Adapter Module 1483? I am using camera HXC13 Baumer and I don't know how to implement communication with CameraLink between camera and FPGA so that I can send configuration commandos (for example :d? for acquiring and changing resolution). I would appreciate any help.

Camera Configuration with CameraLink

Diagnose BNC-2110

Hello,

I am working with a BNC-2110 block and I read the signal in LabView. The problem is my Ch1 does not give as a strong a signal as the Ch0.

How can I check if there is something wrong with the BNC connectors?

Regards.

problem with DI PXI-6509

Hello,

I'm using a PXI-6509 connected to SCB-100 to control some DIO. I have connected the pin 51-53-...-65 to some leds and then to the GND (pin 50) of the board and everything is fine.

Instead I have a very strange behaviour trying to use port 0 (I tested also port 3 obtaining same behaviour) to read some DI.

That's what happens looking from the test panel in MAX. (I performed this test with the DO connected to the board and without)

I force all the lines to 0 by connecting GND to each pin (47-45-...-33). (Some lines were to 1)

After some second (15 more or less) line 7 become high, even if I reforce the line to 0 continues to happen.

If I try to force a pin to 1 by connecting the 5V source of the board (pin 49) random lines go to 1. E.g. touching pin 47 (line 0) I see line 0-1-3-5-6-7 going to 1.

The strangest thing is that is not even constant: thouching pin 47 a second time (with all the lines 0) brings to one lines 0-1-5-6-7 or maybe each line to 1.

Same behaviour (random lines going to 1) for all the other lines of port 0, as I said also for port 3. I did not procede with other tests.

I'm getting a bit confused...

Last fact: port 0 is working as DO, if I change the pin mode to output I can measure 5V correctly with the multimiter.

Any idea of what's going on?

PXI 6555 Singal Routing

Hi

I want to generate a singal via PXI 6555, and make this singal as the external trigger source of another card in a same PXI chassis. So I want to route this singal through PXI trigger line. I can route singal from PFI0 to PXITrig0 using function "niHSDIO_ExportSignal", but my generated singal is on channel DIO0, how can I do the route? Thanks.

What is the input voltage range for NI 5771 digitizer?

Hi,

Can anyone please tell me what is the input voltage range and offset control for NI 5771 digitizer.

Thanks,

Calibration mode differs from in VI collection

I am using a SCXI-1100 module for data collection within a VI. I would like to measure the voltage across a shunt resistor and I need to know the voltage with precision of a tenth of a milivolt or better.

In order to measure the voltage accurately, I have been performing the manual calibration that I can access through the DAQ assistant under callibration. In this callibration mode, the module performs well. The data collected for callibration matches within 00.02 mV with the callibration standard, however when I finish the callibraiton and try to get voltage measurements in the VI, the system performs poorly with a consistent offset of about 0.5 mV.

Is there a reason that the data collected in calibration mode does not match the data collected in the VI? When I've run the calibraiton, I've used the same settings as I run the data acuisisiton at in terms of number of points and frequency of data collection. I could ap

Electrodes as sensor

Hi!

I just want to know, what kind of circuit that I need to use for making a simple ECG, EEG and EMG device using labview as the software and mydaq for data acquisition device. Thanks for the answer.

Generating sample clock of lower frequency HSDIO

I have a PXI-6541 card which is used for digital outputs. I can use the onboard clock of this card to time the output at a clock frequency of 25MHz. I have other cards, a PXIe-6341, PXI-6723 and PXI-4462 used for analog inputs and outputs that need a clock frequency of around 100 kHz. I would like to somehow use the clock from the 6541 card to properly synchronise the cards. Is there a way I could generate a clock signal of a lower frequency on a PFI channel from the 6541 card or do I need to use an output channel.

Alternatively, if I used the 10 MHz clock from the PXIe chassis and had each card sample this at their own frequency would this be enough to ensure the cards are properly synchronised?

Many thanks

Generate and acquire data with marker (HSDIO)

HI. I use PXIe-6556. What i do:

1). Export Onboard clock to DDC CLK OUT. I connected physically PFI4 to PFI3.

2). Then I use script to generate data. In script I use marker (PFI2).

3). And I want acquire data when marker appears. But instead this i have mistake:

niHSDIO Fetch Multi Record (WDT).vi<ERR>Driver Status: (Hex 0xBFFA4020) Some or all of the samples requested have not yet been acquired. To wait for the samples to become available, use a longer read timeout or read later in your program. If your session uses a trigger, make sure that your trigger is configured correctly.

Status Code: -200284

Please help what i do wrong?

NI USB 6525 Limitations

Hi all,

So ive run into a problem with the USB 6525. I am using it as relay to power a solenoid on and off. But i have found that the swithing rate has a max of 2.5 Hz. I had desired to get at least 3 Hz and in some cased even more. Would any one be able to recommend a device that would have this capability. It would be preferable for the device to be USB.

Thanks.

Periodically Extract Payload from CANBus Frames using cRIO in FPGA mode

Hi All,

I am new to LabVIEW and NI products and I'm trying to accomplish the following (I expected this to be simple to do!):

I have a bunch of CAN devices (let's say 12 of them) and I'd like to periodically read data from them. To do so, I write a certain frame (as specified in one of the device's datasheets) to set them all in operational mode. I only need to this once. To read data, I have to write a frame requesting the data and then read the frame I receive, and extract its payload. I set the bus speed to the maximum possible which is 1 Mbit/sec. I think each frame has around 109 bits max (based on the datasheet too), so my expectation is that 250 microsecond is more than enough for one request and receive operation.

Since I am using cRIO9022 (cRIO-9114 chassis) and a NI 9853 CAN module, I was not able to run in scan mode, which seems to be easier to do from the tutorials I saw. I had to run in FPGA mode, and so I used the section 5 in the following tutorial: http://www.ni.com/tutorial/11198/en/ combined with code from "CAN Basic (FPGA).vi" example code to come up with something. I have no problem sending and receiving the frames I want and extracting data, but I'm having trouble writing data to a file using a fixed sample rate and in real-time.

I have two files, the first runs on the FPGA target. It continuously runs, requesting data from the 12 elements, extracting data from the received frames and writing that to a FIFO once I read from all 12 devices. What I'm trying to do in my code is to only spend 250 microseconds to do a request/read operation. I don't know if I implemented correctly, and I'm not sure if the hardware is actually reading every 250 microseconds although I expect it to. I'm not sure how to debug that either.

The second program runs the FPGA target program and sets the send/receive period for it. It's supposed to record data for a set recording time and write it to a tdms file. It somewhat works but what's happening is that the data is not actually always real-time. If I set the frame send/receive period to 250us, it records for a longer time (probably another timing issue in my code). If I set it to 800 us, it seems to match real time as expected. If I set it to more, it records for a shorter amount of time. I tried recording the time elapsed and things don't seem to be timed as I expect.

I attached the code, I think it's simple and has enough comments. It has the project file and VIs. I included the CANOpen communication datasheet for the device(s) I'm reading from. I also included a sample log file. Rows 2 to 12505 are the data measurements and the remaining ones are "timestamps" (taken based on write-to-file time) for 12 measurements.

Please let me know if anything need clarification. I need help resolving my timing issues, or if you can recommend any easy way to do this. I can't be the first one trying to periodically extract and log payload from a CANBus!

Your help is appreciated!

Thanks

如何通过数字波形法从数字IO口产生多路时序脉冲来控制不同继电器的开断

大家好,我刚开始学labview,使用的是NI-USB6259板卡,想通过数字波形法从数字IO口产生5路时序脉冲来控制不同继电器的开断,由于各个时序的间隔和脉宽时间要求都比较高,而计数器只有两个,因此无法完全用计数器输出实现。但有不知道如何通过数字IO实现。求教各位给个范例。谢谢Orz

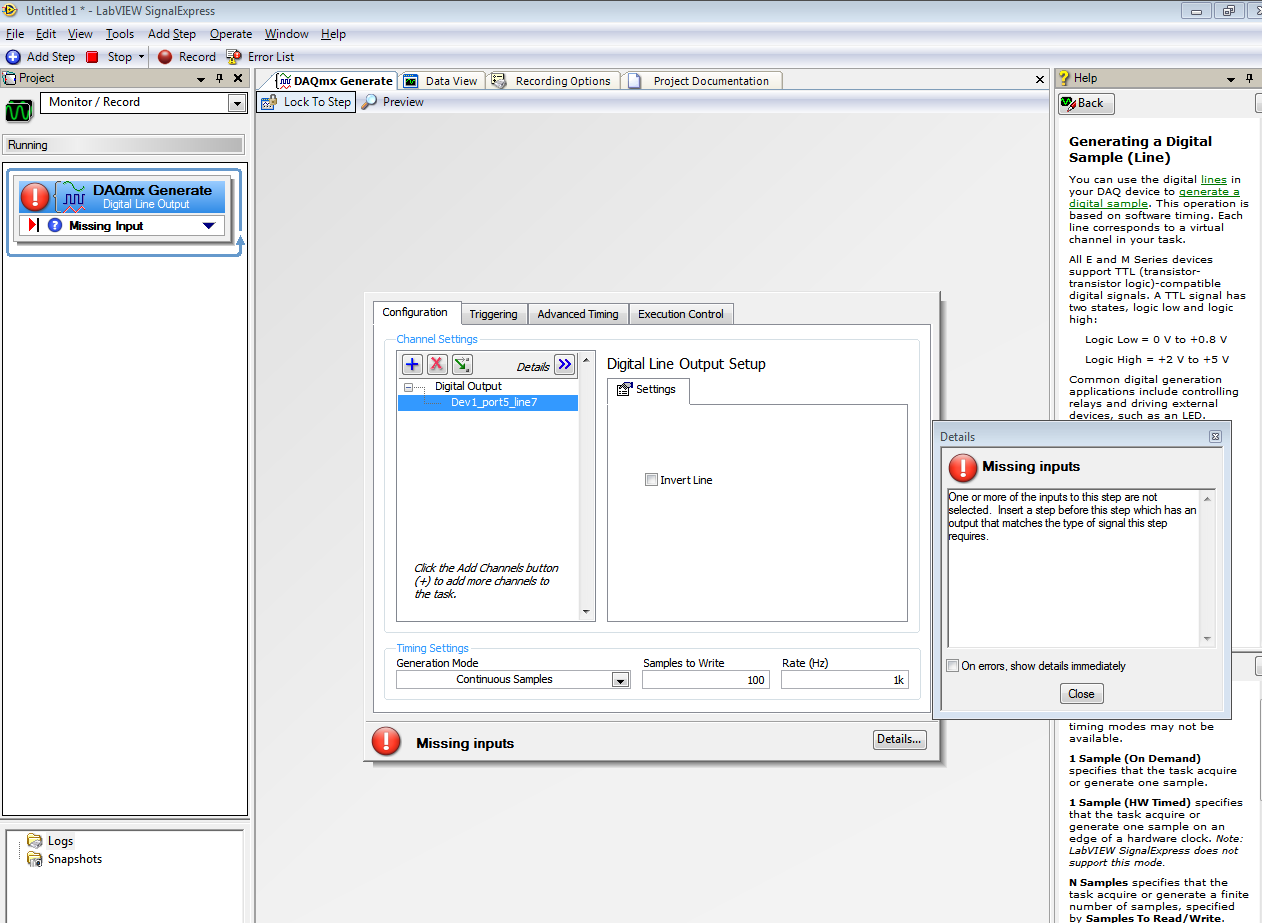

Generating a Digital High/Low output signal on Ni-6528

Hello,

I was wondering if someone could help me. I'm having trouble generating a logic LOW output with my NI-6528 and LabView Signal Express LE.

When I configure continuous signal, I don't get the option to configure my signal to be HIGH or LOW. Also, I get an erorr regarding missing inputs. Does anyone have any ideas or helpful links? I've attached the screenshot below.

Thanks in advance to anyone who can help!

Jenny

NI USB-6501 5V Current

Hello,

The data sheet for USB-6501 indicates that the max current for the 5V output is 230ma. Does anyone know if the max current is 230ma for each 5V output(there are 2) or is it 230ma total?

Thanks,

NI 9476 only DO0-DO8 are working

I have a NI 9476 in a cRIO 9025. I've been programming an application and I noticed that if I wrote to DO13 I would alreays read a false value. I could never set it true.

So I hooked up a 24V LED and wired the supply properly to see if the output was actually working. It wasn't, and it turn out that only DO0-DO8 are working. The rest do not even though I can read back the state I set in all the channels except for DO13.

The LED was the first time the NI 9476 has been connected to hardware. Is this likely to be a faulty NI 9476 or perhaps a driver issue. NI-RIO 15 is installed.

John

Need help with digital output on NI USB-6501 (why does writing bits on one port affect bits on another port?)

Hi,

I'm starting writing code (in C) for the NI USB-6501 and it seems like I'm facing a situation where writing to lines on one port will affect lines on another port. I'm probably doing something wrong or there is some fundamental channel/port/task concept I don't understand... I tried searching the forums for an explaination but with no success.

Details:

What I am trying to acheive is simple: I want to either set the 3 first bits of port0 or the 3 first bits of port1. When I set the bits on one of the ports, I want the bits on the other port to stay the same. So for example, at one point my application will get executed to set the port0 lines to 00000000, then a bit later my application is executed again but this time to set the port1 lines to 00000001 (but I want to keep port0 as-is).

So when I write the 3 first bits of port 0, all good, the bits on port 0 are set correctly (they are all low).

But then when I write the 3 first bits of port 1, the 3 first bits of port 1 are set correctly ** but the 3 first bits of port 0 are also affected and they all change to 1's?! **

Is this normal?

My code looks like this (it does not return any errors so I removed the error handling code for clarity):

void write_to_port_0(uInt8 bits)

{

// Task parameters

int32 error = 0;

TaskHandle taskHandle = 0;

char errBuff[2048];

// Channel parameters

char chan[64];

// Write parameters

uInt8 w_data [1];

int32 written;

sprintf(chan, "Dev1/port%i/line0:3", 0);

printf("Channel: %s\n", chan);

// Create Digital Output (DO) Task and Channel

error = DAQmxBaseCreateTask ("", &taskHandle);

printf("TaskHandle: %i\n", taskHandle);

error = DAQmxBaseCreateDOChan(taskHandle,chan,"",DAQmx_Val_ChanForAllLines);

error = DAQmxBaseStartTask (taskHandle);

w_data[0] = bits;

error = DAQmxBaseWriteDigitalU8(taskHandle,1,1,10.0,DAQmx_Val_GroupByChannel,w_data,&written,NULL);

if (taskHandle != 0)

{

DAQmxBaseStopTask (taskHandle);

DAQmxBaseClearTask (taskHandle);

}

return;

}

void write_to_port_1(uInt8 bits)

{

// Task parameters

int32 error = 0;

TaskHandle taskHandle = 0;

char errBuff[2048];

// Channel parameters

char chan[64];

// Write parameters

uInt8 w_data [1];

int32 written;

sprintf(chan, "Dev1/port%i/line0:3", 1);

printf("Channel: %s\n", chan);

// Create Digital Output (DO) Task and Channel

error = DAQmxBaseCreateTask ("", &taskHandle);

printf("TaskHandle: %i\n", taskHandle);

error = DAQmxBaseCreateDOChan(taskHandle,chan,"",DAQmx_Val_ChanForAllLines);

error = DAQmxBaseStartTask (taskHandle);

w_data[0] = bits;

error = DAQmxBaseWriteDigitalU8(taskHandle,1,1,10.0,DAQmx_Val_GroupByChannel,w_data,&written,NULL);

if (taskHandle != 0)

{

DAQmxBaseStopTask (taskHandle);

DAQmxBaseClearTask (taskHandle);

}

return;

}

Anyone else had this issue before?

Thanks,

Andre

Random segmentation fault when linking to nidaqmxbase under Linux (CentOS 7)

Hi,

It seems that a simple C application that links to nidaqmxbase will randomly segfault.

Here is my setup:

C test app:

#include <stdio.h>

#include <stdlib.h>

int main (int argc, char **argv)

{

exit(0);

}

Now if I compile the above using 'gcc test.c' and then run a.out in a loop, it never segaults. All good.

But if I compile the above using 'gcc ./test.c -lnidaqmxbase' then running the generated a.out in a loop will randomly segfault.

I found a topic in the forums that describes similar behavior (http://208.74.204.114/t5/Multifunction-DAQ/Segmentation-Fault-when-linking-with-NIDAQmx-Base-2-0-in-Linux/m-p/392738) but the thread is pretty old so I figure this problem has probably been fixed by now.

Am I the only one having these segmentation fault issues? Maybe someone is able to reproduce this?

Here is my setup:

CentOS Linux release 7.2.1511 (Core)

Linux Nrc-006933.ds.nrc.ca 3.10.0-327.22.2.el7.x86_64 #1 SMP Thu Jun 23 17:05:11 UTC 2016 x86_64 x86_64 x86_64 GNU/Linux

gcc (GCC) 4.8.5 20150623 (Red Hat 4.8.5-4)

Product: NI USB-6501

Driver installed from: http://ftp.ni.com/support/softlib/multifunction_daq/nidaqmxbase/15.0/linux/nidaqmxbase-15.0.0.iso

(Device firmware successfully updated after driver installation.)

Thanks!

Andre

Using DAQmxWriteDigitalScalarU32 to write channels sharing same port(s)?

Hello,

I have a USB-6509 and NI-DAQmx 15.5.1 installed. Using the ansi c api.

Is it possible to create several independent channels that use different lines from the same port?

DAQmxCreateTask("",&th1)

DAQmxCreateDOChan(th1,"Dev1/line0:4","",DAQmx_Val_ChanForAllLines)

DAQmxStartTask(th1)

DAQmxCreateTask("",&th2)

DAQmxCreateDOChan(th2,"Dev1/line5:9","",DAQmx_Val_ChanForAllLines)

DAQmxStartTask(th2)

....

and repeat for the following channels:

Dev1/line0:4

Dev1/line5:9

Dev1/line10:14

Dev1/line15:19

Dev1/line24:28

Dev1/line29:33

So I can use DAQmxWriteDigitalScalarU32 to write to each task independently?

for example:

DAQmxWriteDigitalScalarU32(th1,1,10,0x1,NULL)

DAQmxWriteDigitalScalarU32(th2,1,10,0x2,NULL)

DAQmxWriteDigitalScalarU32(th3,1,10,0x3,NULL)

...

DAQmxWriteDigitalScalarU32(th6,1,10,0x6,NULL)

Will these tasks interfere with each other since they use the same port, but are assigned different lines?

If not, do I need to bit shift the data if the task/channel doesn't start at line Px.0?

Thanks!

HSDIO Advance trigger

In the example to HSDIO Dynamic Acquisition of Multiple Records.vi used Advance trigger. I have some questions on its application:

1). If we have a trigger, for example, which appears with a frequency of 1 MHz, data each time (when front appears) are received, i.e. there are no gaps in the data acquiring? Can it happen that we will acquire data on the 1st trigger, 5th, 9th, and so on?

2). What is absolute timestamp in waveform information? This is the start time of each record HSDIO?

FlexRIO 6581 Drive Capability

Hi,

From the datasheet of the 6851 card, the IO buffer performance should be that of TI SN74LVC8T245. However I'm seeing issues with the drive of this card doing a simple loopback test.

I have the Internal Card Supply 3.3V set up:

e.g. DDCA Port0 is configured as Write and output port and write a clock out (010101..) on P0.0, I attach the breakout board (NI CB/SCB-2162) to the end of it and I can see the correct clocking data on a scope attached to the breakout board.

If I have DDCA Port1 configured as Read and read data on P1.1 as soon as I connect P0.0 to P1.1 the clocking data out on P0.0 gets pulled down.

From a hardware point of view the 6851 signal on P0.0 sees a load of the VHDCI cable in the first condition and the data out is fine with scope on the breakout board pin. Connecting P1.1 doubles this load, (i.e. adding a return through the cable to the 6851 P1) Should this increased oad be enough to pull the signal down?