Hi

What are the max practical limits for the sample clock using the Shielded Single-Ended Flying-Lead Cable?

I am playing with the Labview embedded example "Dynamic Generation and Acquisition Source Synchronou.vi" using the Shielded Single-Ended Flying-Lead Cable and the PXIe-6556.

This example write in the channels 0-7 and read in the channels 7-15.

It also export the sample clock and data active event so we have a "Source Synchronous"

I change the original example to set the input impedance to 50ohm and VH and VL voltatages.Write 3.3V - 0V and read 0.5V 0.3V.

The problem is the signal integrity at higher frequencies. Please see the picture attached.

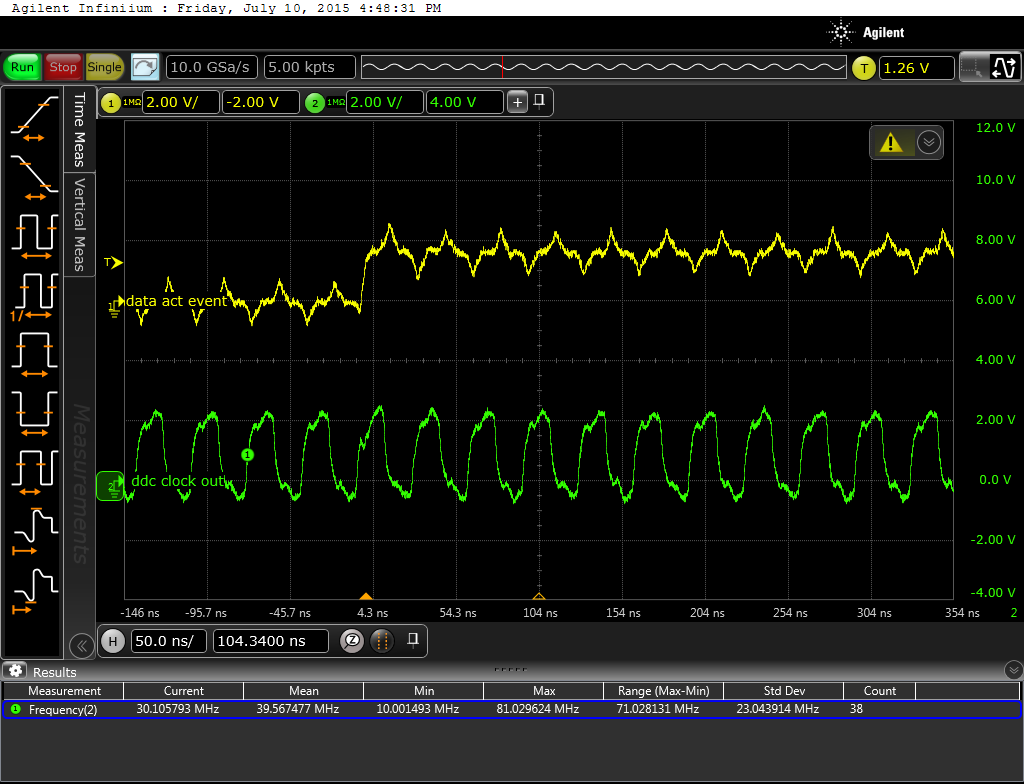

Sample clock 30MHz

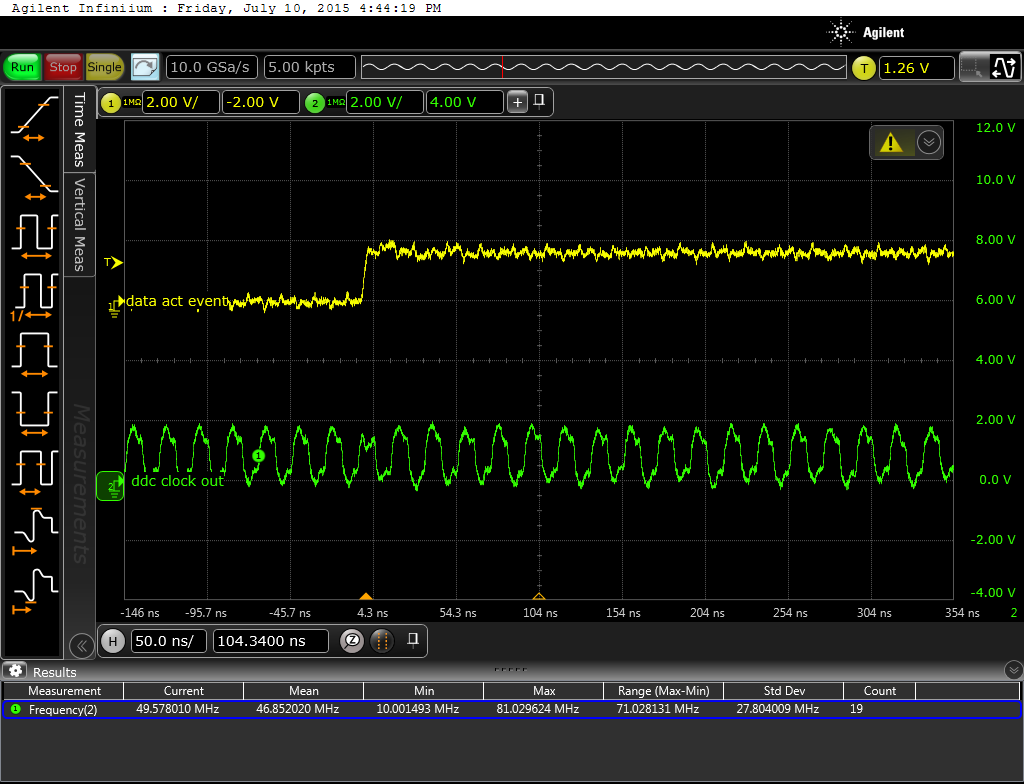

50MHz

70MHz

90MHz

Error: PLL could not phase-lock to the external reference clock.